# HML: AN INNOVATIVE HARDWARE DESCRIPTION LANGUAGE AND ITS TRANSLATION TO VHDL

# A Thesis

Presented to the Faculty of the Graduate School of Cornell University

in Partial Fulfillment of the Requirements for the Degree of Master of Science

by Yanbing Li

August 1995

© Yanbing Li 1995 ALL RIGHTS RESERVED

#### ABSTRACT

HML (Hardware ML) is an innovative hardware description language based on the functional programming language SML (Standard ML).

HML is a high-order language that supports polymorphic functions. HML's advanced type system provides many constructs that are important to hardware descriptions but are lacking in the more mature, widely used hardware description languages such as VHDL and Verilog. Its succinct syntax provides a simple and concise notion for describing hardware.

HML programs do not need to specify types and interfaces while describing hardware; they are automatically inferred using advanced type checking and type inference techniques.

We have implemented an HML type checker and a translator to VHDL. The HML-to-VHDL translator automatically infers types and interfaces and generates a synthesizable subset of VHDL. This makes it possible for users to describe hardware in HML and still be able to make use of the rich availability of VHDL tools or to integrate with other VHDL packages or programs.

Examples are given to illustrate the HML system.

# Table of Contents

| 1 | Introduction           |                                                    |    |  |  |  |

|---|------------------------|----------------------------------------------------|----|--|--|--|

|   | 1.1                    | Purpose                                            | 2  |  |  |  |

|   | 1.2                    | Comparison of HML to other HDLs                    | 2  |  |  |  |

|   | 1.3                    | Preview                                            |    |  |  |  |

| 2 | $\mathbf{H}\mathbf{M}$ | IL Language                                        | 7  |  |  |  |

|   | 2.1                    | Introduction                                       | ,  |  |  |  |

|   |                        | 2.1.1 Introduction to SML                          | ,  |  |  |  |

|   |                        | 2.1.2 Introduction to HML                          | 8  |  |  |  |

|   |                        | 2.1.3 A Quick Example of HML                       | Ć  |  |  |  |

|   | 2.2                    | HML Types and Objects                              | 10 |  |  |  |

|   |                        | 2.2.1 HML Basic Types                              | 11 |  |  |  |

|   |                        | 2.2.2 Advanced Types                               | 12 |  |  |  |

|   |                        | 2.2.3 HML Objects and Object Declarations          | 14 |  |  |  |

|   | 2.3                    | HML Programming Constructs                         | 16 |  |  |  |

|   |                        | 2.3.1 HML Lexical Elements                         | 16 |  |  |  |

|   |                        | 2.3.2 Signal Assignments                           | 16 |  |  |  |

|   |                        | 2.3.3 Expressions and Operators                    | 17 |  |  |  |

|   |                        | 2.3.3.1 Operators                                  | 18 |  |  |  |

|   |                        | 2.3.3.2 Bit-vectors Operations                     | 19 |  |  |  |

|   |                        | 2.3.3.3 Behavioral Operators                       | 20 |  |  |  |

|   |                        | 2.3.3.4 Expressions                                | 21 |  |  |  |

|   |                        | 2.3.4 Function and Hardware Function Declarations  | 22 |  |  |  |

|   | 2.4                    | Describing Hardware in HML                         | 23 |  |  |  |

|   |                        | 2.4.1 Describing Structure in HML                  | 24 |  |  |  |

|   |                        | 2.4.2 Describing Behavior in HML                   | 26 |  |  |  |

|   |                        | 2.4.3 Putting Behaviors and Structures Together    | 27 |  |  |  |

|   |                        | 2.4.4 Restrictions of Describing Hardware in HML   | 27 |  |  |  |

|   | 2.5                    | Discrepancies Between HML and SML                  | 28 |  |  |  |

| 3 | $\mathbf{H}\mathbf{M}$ | IL Type Checking and Inference                     | 30 |  |  |  |

|   | 3.1                    | Introduction                                       | 30 |  |  |  |

|   | 3.2                    | Type Checking and Type Inference Rules             | 3. |  |  |  |

|   |                        | 3.2.1 Definition of Types Used in the Type Checker | 3. |  |  |  |

| Λ |                   | L Grammar                                                                                                                                                                                     | 88                     |

|---|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

|   |                   |                                                                                                                                                                                               |                        |

| 7 | Con<br>7.1<br>7.2 | clusions and Future Plans  Conclusions                                                                                                                                                        | <b>8</b> !<br>8!       |

|   | 6.2               | Tools                                                                                                                                                                                         |                        |

| 6 | <b>Exa</b> 6.1    | Mon-restoring Integer Square-root                                                                                                                                                             | 7                      |

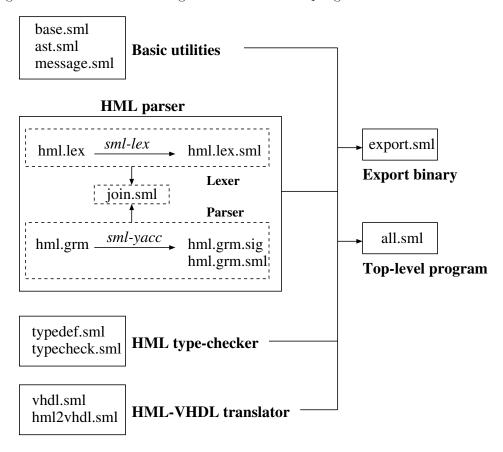

| 5 | Imp<br>5.1<br>5.2 | lementation in SML Organization of HML Source Programs                                                                                                                                        | <b>6</b> 8<br>68<br>67 |

|   | 4.4               | 4.3.2 High-order Functions                                                                                                                                                                    | 58<br>63               |

|   | 1.5               | 4.3.1 Recursive Functions                                                                                                                                                                     | 58                     |

|   | 4.3               | 4.2.6 Other Issues in the Translation                                                                                                                                                         | 50<br>5'               |

|   |                   | 4.2.5 Translation for Simulation and Synthesis                                                                                                                                                | 53                     |

|   |                   | structs                                                                                                                                                                                       | 49<br>5<br>5           |

|   |                   | <ul> <li>4.2.1 Top-level Translation</li></ul>                                                                                                                                                | 4:                     |

|   | 4.2               | HML-to-VHDL Translation Rules                                                                                                                                                                 | 4:                     |

|   |                   | <ul> <li>4.1.1 VHDL Overview</li> <li>4.1.2 The VHDL Subset Used in the HML-to-VHDL System</li> <li>4.1.3 Introduction to Mentor-Graphics VHDL Simulation/Synthesis</li> <li>Tools</li> </ul> | 3:<br>4:<br>4          |

|   | 4.1               | Introduction to VHDL                                                                                                                                                                          | 3                      |

| 4 | Trai              | nslating HML to VHDL                                                                                                                                                                          | 39                     |

|   | 3.3               | 3.2.3 Type Inference Rules                                                                                                                                                                    | $\frac{3}{3}$          |

|   |                   | 3.2.2 Environments                                                                                                                                                                            |                        |

Bibliography 95

# List of Tables

| 1.1 | Comparisons of HML and other hardware description languages | S  |

|-----|-------------------------------------------------------------|----|

| 2.2 | HML Types                                                   | 17 |

|     | The VHDL subset that is used in HML-to-VHDL system          |    |

# List of Figures

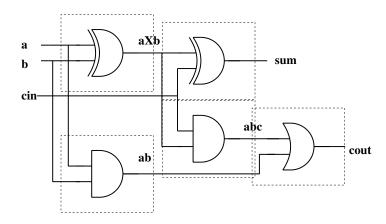

| 2.1  | Gate level circuit diagram of a full adder                                                  | 6             |

|------|---------------------------------------------------------------------------------------------|---------------|

| 2.2  | Structural description of a 1-bit fullAdder                                                 | 10            |

| 2.3  | Behavioral description of a 1-bit fullAdder                                                 | 10            |

| 2.4  | HML description of an adder with carry output using bit-vector                              |               |

|      | concatenation                                                                               | 20            |

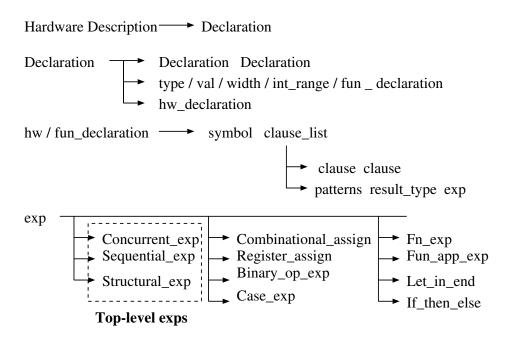

| 2.5  | HML programming constructs and program organization – a simplified HML abstract syntax tree | 24            |

| 2.6  | Example: A polymorphic array generator                                                      | 25            |

| 2.7  | An n-bit full adder generator based on a 1-bit full adder                                   | 26            |

| 2.8  | Example: A polymorphic adder with latched output                                            | 26            |

| 2.9  | Rewrite the polymorphic adder with latched output by mixing                                 |               |

| 2.0  | structural and behavioral descriptions                                                      | 27            |

| 2.10 | Example of multiple assignments to one signal                                               | $\frac{2}{2}$ |

| 2.10 | Example of multiple assignments to one signar                                               | (             |

| 3.1  | Definition of types: modes and pure types                                                   | 32            |

| 3.2  | HML type checking and type inference rules                                                  | 33            |

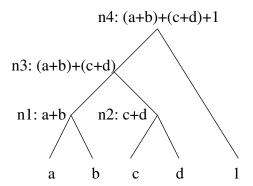

| 3.3  | Abstract syntax tree segment for expression $(a+b)+(c+d)+1$                                 | 37            |

| 4 1  |                                                                                             | 4             |

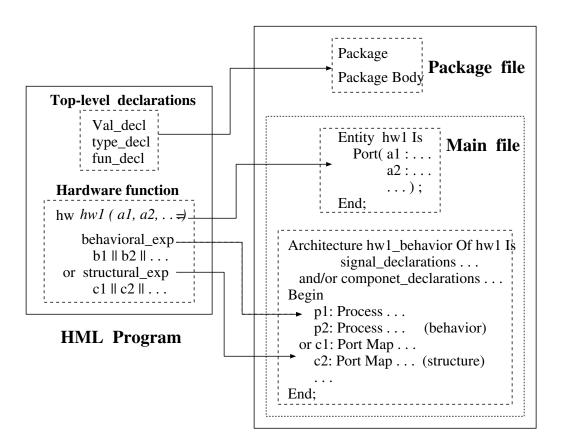

| 4.1  | HML-to-VHDL Top-level Translation Graph                                                     | 44            |

| 4.2  | Translated VHDL description for the fullAdder example – structure                           | 46            |

| 4.3  | Translated VHDL description for the fullAdder example – behavior                            | 47            |

| 4.4  | Translated VHDL description for an adder with output latch (mix-                            | 10            |

| 4 -  | ture of structural and behavioral description)                                              | 48            |

| 4.5  | Translated VHDL description for the simple adder sum                                        | 50            |

| 4.6  | Translation of signal assignments                                                           | 51            |

| 4.7  | Translation of functions: Example of a 4-bit counter                                        | 54            |

| 4.8  | Different translation for simulation and synthesis                                          | 55            |

| 4.9  | Object renaming in HML-to-VHDL translation                                                  | 58            |

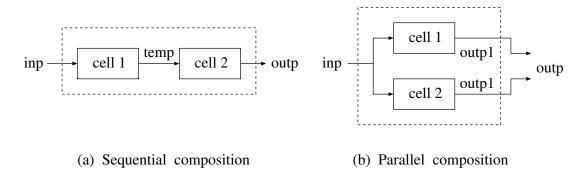

| 4.10 | Two high-order structural compositions                                                      | 59            |

| 4.11 | HML descriptions for two high-order structural compositions                                 | 60            |

| 4.12 | Translated VHDL descriptions for sequential compositions                                    | 61            |

| 4.13 | Translated VHDL descriptions for parallel composition                                       | 62            |

| 5.1  | Organization of HML source programs                                                         | 66            |

| 6.1  | Non-restoring integer square root Level 2 algorithm in SML                                  | 73            |

|      |                                                                                             |               |

| 6.2  | HML description of integer square root Level 2 algorithm       | 74 |

|------|----------------------------------------------------------------|----|

| 6.3  | VHDL description of integer square root produced by VHDL-HML   |    |

|      | translator – Simulation Version                                | 76 |

| 6.4  | QuickVHDL simulation stimulus file of square root example      | 77 |

| 6.5  | Simulation wave form of square root example                    | 77 |

| 6.6  | VHDL description of integer square root produced by VHDL-HML   |    |

|      | translator – Synthesis Version                                 | 78 |

| 6.7  | HML description of an adder/subtracter ALU                     | 80 |

| 6.8  | VHDL description of the adder/subtracter ALU produced by VHDL- |    |

|      | HML translator (Part 1, to be continued)                       | 81 |

| 6.9  | VHDL description of the adder/subtracter ALU produced by VHDL- |    |

|      | HML translator (Part 2, continued)                             | 82 |

| 6.10 | VHDL description of the adder/subtracter ALU produced by VHDL- |    |

|      | HML translator (Part 3, continued)                             | 83 |

# Chapter 1

# Introduction

Hardware description languages (HDLs) are used to describe hardware for the purpose of simulation, modeling, testing, design, and documentation of digital systems. They are playing an important role in computer-aided design. With the progress of synthesis technology, the abstraction level of the description is getting higher. We present HML, which has a higher level of abstraction than most of the widely used HDLs.

HML is a functional hardware description language based on Standard ML (SML) [MTH90]. SML is a high-level functional programming language which is strongly typed and polymorphic and supports high-order functions. HML inherits many programming features of SML and takes advantage of many advanced techniques that are adopted from SML, including the rich type system, advanced type-checking and type inference. It also includes extensions for describing hardware, such as the concept of signal and the definition of hardware functions.

HML can be easily integrated with different back ends such as simulators and tools for hardware synthesis and verification.

# 1.1 Purpose

The major motivation for designing HML is to have a concise and powerful notation for hardware description. HML's high-order and advanced type system, which includes polymorphism and automatic type inference, makes this possible. As more designs are used in synthesis, it is also desirable to have a hardware description language suitable for synthesis. Among the existing HDLs, most of them have only a subset that is synthesizable.

HML was designed based on these considerations. Firstly, the most prominent feature of HML is that the automatic inference of types and interfaces allows users to write programs without specifying types. This makes HML programs easy to write and read. Secondly, strong type checking allows the user to find design rule violations such as bus width mismatches early in the design process. Thirdly, HML provides many constructs that are important to hardware description but are lacking in the more mature, widely accepted hardware description languages. Describing hardware at a higher level, HML is able to take advantage of many recent techniques in programming language research such as high-order functions and polymorphism that are not included in existing languages such as VHDL [IEE88], Verilog [TM91], and Ella [MPT85]. Finally, because more and more designs are aiming at synthesis, we implemented an HML-to-VHDL translator which allows users to write HML programs which generate synthesizable VHDL programs that can be simulated and synthesized on the commercially available VHDL tools or can be integrated with other VHDL programs.

# 1.2 Comparison of HML to other HDLs

There are many hardware description languages that are widely accepted; why do we need HML? The comparison of HML to other HDLs shows that HML has its

advantages. We have compared HML to VHDL, Verilog, Ella and Ruby.

Created to be a standard, VHDL [IEE88] has a very comprehensive syntax that combines both general computing and hardware description. It can support descriptions at different levels (behavioral, register transfer and structural). However, there is a subset of VHDL which doesn't have explicit hardware meaning and is theoretically not synthesizable.

VHDL is strongly typed and allows designer to specify their own enumerated types and subtypes. Since VHDL's type system is much more restrictive than that used in HML, many useful functions for hardware description cannot be written in VHDL. One such construct is a hardware generator that generates the same regular structure independent of the types of the ports of its submodule; the HML generator code is reusable on different types of submodules. VHDL doesn't support polymorphic functions; the user has to write a separate generator function for each type of the submodule. VHDL does not support recursive functions and high-order functions, which are very useful in describing hardware. In VHDL, all types and interfaces must be specified by the designer. In HML, types and interfaces are inferred automatically.

Another widely used hardware description language, Verilog [TM91], includes only a very limited notion of data types. Verilog does not allow user defined types or enumerated types, although it does allow subranges to be defined. Many of the design errors found by type checking strongly typed languages such as HML and VHDL will not be found in designs described using Verilog.

Ella [MPT85] is perhaps the HDL which is the most similar to HML. Ella is a functional language which supports user defined, enumerated types. However, all types must be specified by the designer - no attempt is made to infer types. Ella does support recursive functions but its typing system is not polymorphic, so regular structure generators with type inference cannot be specified with Ella.

Ruby [JS90] is a notation and design discipline intended for the development of regular integrated circuits and similar hardware and software architectures. The general idea of Ruby is that circuits and circuit components are represented by relations between the signals at their inputs and outputs. Larger circuits are assembled from components by a suite of functions, such as relational composition and various combining forms that represent regular arrays of components. In Ruby, polymorphism is supported by allowing the same development to be applied to many different designs. Ruby supports high-order functions and recursive functions. Ruby provides various compositions for hardware structure, but it doesn't provides features for describing behaviors. The compositions are represented in equations ("algebraic laws") which are succinct in format but are also very hard to read.

The above comparison focused on type systems of the four languages. In addition, HML is superior to other three languages with its succinct and simple syntax, which will be shown by the examples throughout the thesis. Table 1.1 summarizes the comparison of HML to other HDLs.

Table 1.1: Comparisons of HML and other hardware description languages

|                  | VHDL          | $\mathbf{Verilog}$         | Ella                        | Ruby                  | HML                         |

|------------------|---------------|----------------------------|-----------------------------|-----------------------|-----------------------------|

|                  | IEEE          | $\operatorname{Cadence}$   | ${ m Manchester}$           | Oxford                | Cornell                     |

| Origin           |               | Design                     |                             |                       |                             |

|                  | Standard      | $\operatorname{System}$    | $\operatorname{University}$ | University            | $\operatorname{University}$ |

| Based on         | Ada           | C, Pascal                  |                             |                       | $\operatorname{SML}$        |

| Syntax           | Very          |                            |                             | Abstract              | $\operatorname{Simple},$    |

|                  |               | $_{ m Simple}$             | Complicated                 | hard to               | emphasize                   |

| complexity       | complicated   |                            |                             | $\operatorname{read}$ | functionality               |

| Syntax           | Very          | $_{ m Verbose}$            | Verbose                     | Succint               | Succint                     |

| verbosity        | verbose       |                            |                             |                       |                             |

| synthesizability | A subset      |                            | Core                        | Тоо                   | Generate                    |

|                  |               | Yes                        | Ella                        |                       | synthesizable               |

|                  | synthesizable |                            | synthesizable               | abstract              | VHDL subset                 |

| Straightforward  |               |                            |                             |                       |                             |

| hardware         | Partially     | Partially                  | Partially                   | No                    | Yes                         |

| meanings         |               |                            |                             |                       |                             |

| Туре             | User          | $_{ m User}$               | $_{ m User}$                | No                    | Types                       |

|                  | specifies     | $\operatorname{specifies}$ | $_{ m specifies}$           |                       | $\inf$ erred                |

| inference        | types         | $_{ m types}$              | ${ m types}$                | types                 | automatically               |

|                  |               |                            |                             |                       | Functions can               |

| Polymorphic      | No            | No                         | No                          | Yes                   | apply to                    |

|                  |               |                            |                             |                       | multiple types              |

| High order       | No            | No                         | No                          | yes                   | Functions are               |

|                  |               |                            |                             |                       | first-class types           |

|                  | Rich          | Rich                       |                             | a small               | Translated to               |

| Tools            |               |                            | available                   |                       | m VHDL,~use                 |

|                  | availability  | availability               |                             | $\operatorname{set}$  | VHDL tools                  |

# 1.3 Preview

HML was first described in a paper [OLLA93] which discussed HML features and how to use it to describe structural hardware. In a later paper [OLHA95], HML was used to describe the behavior of a non-restoring square root example. There was no HML parser and type checker available at that time.

In this masters work, I modified some old definitions of HML [OLLA93], added new features such as hardware functions, and did the implementation of the HML system. I have implemented a front-end HML parser, a type-checker which automatically infers types and interfaces and also checks for syntax and typing errors

and some design rule errors, and an HML-to-VHDL translator which translates HML programs into synthesizable VHDL programs.

This thesis is organized as follows. Chapter 2 gives a detailed description of the HML language, its programming features, syntax and informal semantics, particularly hardware meanings. Chapter 3 discusses the type checking / type inference rules and the algorithms that are used in the HML type checker. Chapter 4 covers the HML-to-VHDL translation rules, based on the informal semantics and hardware meanings of HML constructs that are described in Chapter 2. Chapter 5 addresses the actual implementation of the system in SML. It explains the organization of the source programs and the function of source programs. Chapter 6 gives two illustrating examples of HML. The programming techniques discussed in Chapter 2 are used to describe an integer square-root and an add/subtract example. Chapter 7 summarizes the work and discusses future directions.

There are 3 appendices. Appendix A is a summary of the HML grammar. Appendix B is the user's manual for using the HML2VHDL system. Appendix A and B together with Chapter 2 can serve as a thorough HML system manual. Appendix C is the list of all the signatures that are used in the system source code. Along with Chapter 5, it is a guide for reading and modifying the source code.

# Chapter 2

# HML Language

This chapter gives a detailed description of HML features, syntax, and an informal semantics. The introduction provides some background information on the Standard ML programming language (SML) and an overview of HML. The next two sections discuss HML's type system and programming constructs. The last section in this chapter is about how to describe hardware (including structural and behavioral descriptions) in HML and some programming techniques.

# 2.1 Introduction

HML is based on SML [MTH90], including extensions in the area of hardware descriptions. It is also implemented in SML of New Jersey. The first part of this section briefly introduces SML, the second part is an overview of HML.

#### 2.1.1 Introduction to SML

SML (Standard ML) is a very high level programming language and is based upon a formal definition [MTH90] that prescribes the precise semantics of the language. SML is primarily a higher order functional language. SML is strongly typed and polymorphic. This retains much of the flexibility of typeless languages while preventing most run-time type errors. SML's modules may be the most advanced of any language. The SML functor extends the usual notion of generic module. SML does support some procedural programming features, such as sequential operations, assignments, references, input/output commands and exception handling [Pau91].

There are several different implementations of SML available. One of the best and most widely used implementations is Standard ML of New Jersey (SML-NJ) [AT93]. SML-NJ produces efficient code and includes a variety of tools to support program development. Among those tools which were used with the HML system are: SML-Lex and SML-Yacc. Lex and Yacc provide the capability of reading input files and parsing them into a data structure.

#### 2.1.2 Introduction to HML

HML adopts many advanced features from SML, including:

- Functional language, with some procedural programming features,

- high-order and polymorphic functions,

- automatic type inference, and

- concise and readable syntax.

HML inherits a subset of its syntax from the programming language SML. This includes type, value and function declarations, expressions and program control statements. HML also supports non-functional features such as sequential expressions and assignments in similar ways to SML.

In addition, HML adds important features specifically for hardware description, including the concept of signals, behaviors and hardware functions, logic operators, and behavior and structure constructors.

# 2.1.3 A Quick Example of HML

In this section we look at a small example of an HML description of a 1-bit full adder to get a feel for how to use the language for describing hardware. In the following sections of this chapter, we will discuss the HML type system, programming constructs and in greater detail, how to describe hardware using HML.

The 1-bit full adder has three inputs: a, b and carry input cin; it has two outputs: sum and cout. The formulas for calculating sum and cout are:

$\begin{aligned} & \texttt{sum} & = a \oplus b \oplus cin \\ & \texttt{cout} & = a \times b + a \times cin + b \times cin = a \times b + cin(a \oplus b). \end{aligned}$

The gate level design according the the above formulas is shown in Figure 2.1.

Figure 2.1: Gate level circuit diagram of a full adder

HML can describe hardware in structural and behavioral formats. Figure 2.2 gives the description of the 1-bit full adder in the structural format. hw is the keyword for defining a hardware function. cin, a, b, sum and cout are the arguments of the hardware function, representing the interface of the adder. Inside the hardware function, structures are built from modules and signals. Gates AND, OR and XOR are pre-defined modules; they are composed together by operator "||". Signals with the same name are connected. aXb, ab and abc are internal signals declared by the intern declaration.

```

hw fullAdder (cin, a, b, sum, cout) =

let

intern aXb, ab, abc

in

XOR (a, b, aXb)

|| XOR (cin, aXb, sum)

|| AND (cin, aXb, abc)

|| AND (a, b, ab)

|| OR (ab, abc, cout)

end

```

Figure 2.2: Structural description of a 1-bit fullAdder

Figure 2.3 gives the behavioral description of the full adder. The behavior description is the direct translation of the formulas for calculating sum and cout. It consists of two signal assignments (each is a behavior) composed together by a behavior operator "||" (same as that for structure).

```

hw fullAdder (cin, a, b, sum, cout) =

sum := a xor b xor cin

|| cout := (a and b) or (cin and (a xor b))

```

Figure 2.3: Behavioral description of a 1-bit fullAdder

# 2.2 HML Types and Objects

The advanced type system is HML's most prominent feature compared to other hardware description languages. HML is strongly typed yet polymorphic. This makes HML functions more flexible and at the same time strong type-checking prevents run-time type errors and some design rule violations. Automatic type inference gives users the convenience of not specifying types. Section 2.2.1 describes the basic types of HML. Section 2.2.2 discusses advanced types built on basic types. Section 2.2.3 explains HML objects and how to declare objects, particularly signals.

# 2.2.1 HML Basic Types

HML provides a number of basic types, including unit, bool, bit, integer and bitvector types. The operators on these types are defined in Section 2.3.3.

- 1. Unit is the most basic type with a single value written as "()". An expression with a value of unit is evaluated as a null expression.

- 2. Bit type has a value of either high written as '1' or low written as '0'.

- **3.** Bool can have a value of either true or false, it is mainly used in the software sense in behavioral description, while bit has a hardware interpretation.

- 4. An *integer* type is a range of integer values within the range specified by declaration range or the default range is used. The syntax of a range declaration is:

### range integer1, integer2

integer1 and integer2 are two arbitrary integers. At the stage of synthesis, integers are synthesized into bit-vectors. The width of the bit-vectors are decided by the range of the integers.

**5.** A *bit-vector* type is an array of *bits*. The width of bit-vectors used in a program can be set by a *width* declaration. The syntax is:

#### width integer1, integer2

integer1 and integer2 are two non-negative integers that represent how the bit-vector is labeled.

Note that in an HML program, range or width declaration can be used only once, as the global integer range or bit-vector width. If an object has different range or width from what is declared by the range or width declaration, it should be specified when the object is introduced for the first time. For example, in the following program segment,

```

width 7,0

hw example (a : bit\_vector(3,0), b, c...) =

```

width 7,0 declares that all the bit-vectors used in this program has width of 8-bit (labeled as bit-vector(7 downto 0)), excepted where noted. a:bit\_vector(3,0) specifies that the width of a is 4-bit (labeled as bit-vector(3 downto 0)).

6. HML has a special type called behavior. It is used in hardware function declarations as the return type. Signal assignments allow behaviors to communicate with each other; they are also the primitives of behavior types. There will be more detailed discussion about behavior type and signal assignments in this chapter.

## 2.2.2 Advanced Types

As a high-order language, HML's functions are first-class objects and can be used in other functions as arguments. Functions have function types which are mappings from a list of types to basic types. The **definition** of function type is as follows.

```

\texttt{function\_type} \ := \ \texttt{type} \ \texttt{list} \ \to \ \texttt{type}

```

The type list at the left side of the  $\rightarrow$  is a list of the input argument types. The type at the right side of the  $\rightarrow$  is the type of the return value of the function.

For example, fun add (a, b) = a + b defines a polymorphic add function with type:  $\alpha * \alpha \to \alpha$ .  $\alpha$  is a type variable who value can be either integer type or bit-vector type. Type variable is used in polymorphic type system to represent unknown types. One of its important applications is to check consistent usage of an object whose type is unknown [ASU86].

SML's function definition is extended to include the notion of hardware function. A hardware function type is the type of a hardware module. It is a mapping from an interface type to a behavior type. The interface type is a list of hardware interface ports, each port is a pair of Input/Output information and type. The Input/Output can have four values: Input means the port is an input; Output means that it is an output; InOut means that it is a bidirectional port; Non\_applied implies that an object is used in the software sense only and therefore does not have input/output meaning. A hardware function returns a behavior type. Here is the definition of hardware types:

```

hardware_type := interface_type → behavior_type

interface_type := (io, type) list

io := Input | Output | InOut | Non_applied

```

In our 1-bit full adder example, the hardware function fullAdder has three inputs a, b and cin and two outputs sum and cout; its type is:

```

(Input,bit) * (Input,bit) * (Input,bit)

* (Output,bit) * (Output,bit) → behavior.

```

Because HML supports high-order functions, the term type used in function\_type and interface\_type can be either basic types or advanced types including function types and hardware function types.

An instance of an HML module (with a hardware function type) is the application of the corresponding hardware function to some signals that it is connected to; it has a behavior type. For example, XOR (a, b, aXb) as an instance of hardware function XOR is of behavior type.

HML allows user defined types. New types can be created with type declarations. A type declaration defines an abbreviation for an enumerated type expression. An enumerated type is an ordered set of identifiers. The identifiers within a single enumerated type must be distinct, they should also be distinct from other identifiers used as variables or signals.

An example of an enumerated type in HML is:

```

type state = add | subtract | multiply | divide .

```

Type state is defined with four possible values.

Table 2.1 gives a summary of HML types.

| $T_{2}$      | ypes          | Descriptions                                |  |

|--------------|---------------|---------------------------------------------|--|

|              | Unit          | ()                                          |  |

|              | Bool          | true, false                                 |  |

| Basic        | Bit           | '0', '1'                                    |  |

|              | Integer       | Range of integers,                          |  |

|              |               | range i, j                                  |  |

| types        | Bit-vector    | Array of bits,                              |  |

|              |               | width i, j                                  |  |

|              | Behavior      | Type of signal assignments                  |  |

|              | Function      | Type of regular functions                   |  |

| Advanced     | type          | function_type = type list $ ightarrow$ type |  |

|              | Hardware      | Type of hardware modules                    |  |

| types        | function type | hardware_fun =                              |  |

|              |               | io_type list $ ightarrow$ behavior_type     |  |

| User defined |               | Enumerated types                            |  |

| types        |               | type t = v1   v2                            |  |

Table 2.1: HML Types

# 2.2.3 HML Objects and Object Declarations

An object is a named item in an HML description which has a value of a specified type. There are two classes of objects: *constants* and *signals*.

**Constants** can be declared with a *val* declaration (value declaration) at the global level. Value declarations assign values to an object, they have the syntax:

$$val id = exp.$$

Signals can also be viewed as a type. They are used to communicate between hardware behaviors in a behavioral description or to connect submodules in a structural design. They have type  $\alpha^{=}$ . The superscript "=" indicates that we require signal values to be of an equality type. If a type can have an equality test as an operation then it is called an equality type. The basic types int, bool, bit, unit and bit-vector are all equality types. On the other hand, any type involving a function type  $(T_1 \to T_2)$  is not an equality type [Rea89].

All the arguments in a hardware function are signals that are visible at a mod-

ule's interface. The signals used internally in a hardware module can be declared by *intern* declarations inside hardware function declarations. The syntax for *intern* declarations is:

```

intern id1, id2, ids ...

```

In the full adder example in Figure 2.2, declaration intern aXb, ab, abc declares aXb, ab and abc to be internal signals that are invisible outside the module.

Signals can also be declared by a *val* declaration, with its initial value set as the value of the *exp* in the *val* declaration. For example, in the following program segment, val in\_signal = 0 declares an internal signal in\_signal of type *int* and sets its initial value to be 0.

```

hw example(...) =

let

val in_signal = 0

in

...

end

```

Only val declarations that appear inside a hardware function declaration declare signals. Global level val declarations declare constants.

Due to HML's automatic type inference system, an object declaration does not have to specify the object's type. However, as an option, the user can choose to specify types of objects. The syntax for specifying types is to add type information when an object is first declared. For example, val in\_signal: int = 0 declares signal in\_signal to have type int. This is the type that would be inferred automatically if it were not declared.

# 2.3 HML Programming Constructs

This section describes the HML programming constructs, including lexical elements, expressions and operators, and declarations. The syntax for these constructs are given. For more details about HML syntax, refer to Appendix A.

### 2.3.1 HML Lexical Elements

#### 1. Comments

Comments in HML are enclosed by "(\*" and "\*)". Nested comments are supported.

#### 2. Identifiers

Identifiers are used as programmer defined names. They must conform to the rule:

$$id : [A-Za-z][A-Za-z_0-9]*$$

#### 3. Bit and Bit Strings

The value of a bit is represented by '0' or '1'. Bit-vectors are arrays of type bit, they are represented by enclosing the bit vector value in double quotes, for example "00011101".

#### 4. Bool Value

The value of Bool type is either "true" or "false".

#### 5. Key words

The following names are reserved for key words: and, and also, bit, bool, bit-vector, case, else, end, false, fn, fun, hw, if, in, int, intern, inv, let, nand, nor, not, of, or, orelse, structure, then, true, type, val, xor, and xnor.

# 2.3.2 Signal Assignments

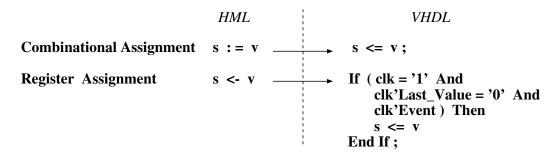

As mentioned in Section 2.2.1, signal assignments are the primitives of behavior type. In HML, signals can be assigned values by two kinds of assignments. Table 2.2 shows their syntax and hardware meanings. The first, combinational

assignment, is intended to model the behavior of combinational logic. The target signal is updated immediately. The second, register assignment, is intended to model the behavior of sequential circuit elements; the target signal is updated in the next clock cycle. Assuming global time t with values of 0, 1, 2, ..., the signal assignment syntax can be seen as a shorthand for the hardware meanings shown in Table 2.2. To keep HML simple, the above signal assignments do not specify any timing information. However, register assignments implicitly include clock information. The HML-to-VHDL translator that we have implemented will prompt users about whether to add timing information to the generated VHDL code. Based on the user's choice, timing information can be automatically added to the VHDL code by the translator. Since timing and clocks do not need to be specified, the programs emphasize functionality and ignore the actual implementation details; they are easier to read or write.

HML only supports one global clock; users can choose the type of the clock while compiling the program. The support for multiple clocks is future work.

Table 2.2: Signal assignment: syntax and hardware meanings

| Combinational<br>Assignment | Syntax<br>Meaning | signal := expression<br>signal(t) = expression(t) |

|-----------------------------|-------------------|---------------------------------------------------|

| Register                    | Syntax            | signal <- expression                              |

| Assignment                  | Meaning           | signal(t+1) = expression(t)                       |

# 2.3.3 Expressions and Operators

An HML expression is a formula combining primitive expressions with operators or with programming constructs such as if..then..else. All the HML operators and their precedence and scope are listed in Table 2.3; they are discussed below.

| Class             | Operators            | Types operated on            |

|-------------------|----------------------|------------------------------|

|                   |                      | & descriptions               |

| Sign              | ~                    | int                          |

| Arithmetic        | * , div              | int, bit-vector              |

|                   | +, -                 |                              |

| Relational        | =,<>,>,=,<,<=        | int, bit-vector              |

| Logical           | and, or, nand, nor,  | int, bit, bit-vector         |

|                   | xor, xnor, inv       |                              |

| Boolean           | andalso, orelse, not | bool                         |

| Bit concatenation | 0                    | bit, bit-vector              |

|                   | ;                    | In behavioral description:   |

|                   |                      | sequential expressions       |

| Behavior          |                      | Submodule composer and       |

|                   |                      | Concurrent behavior composer |

Table 2.3: HML Operators and precedence (in order of decreasing precedence)

#### 2.3.3.1 Operators

The **arithmetic operators** are +, -, \*, and **div**; they operate on values of type integer or bit-vector. Bit-vectors are assumed to be 2's complement representations of integers in these operations.

The **boolean operators** are **not**, **and also** and **orelse**. **and also** and **orelse** are "short-circuit" operators; they only evaluate their right operand if the left operand does not determine the result. They all operate on *bool* type.

The logical operators are and, or, nand, nor, xor, xnor and inv, they operate on values of type *integer*, bit and bit-vector. The operators are bitwise if operating on integers and bit-vectors. Integers are treated as bit-vectors with 2's complement representation.

The **relational operators** =,>,>=,<,<=,<>, are used on values of type *integer* and *bit-vector*. Bit-vectors, are treated as 2' complement representations of integers. = and <> can be also applied to values of type *bit* and *bool* to compare whether the two values are equal.

The **sign operator**  $\sim$  operates on values of *integer* type. Note the difference from "-".

All operators of two operands require the two operands to have the same type.

#### 2.3.3.2 Bit-vectors Operations

Among the operators described in Section 2.3.3.1, arithmetic, logical and relational operators can be used with bit-vectors. Bit-vectors also have some special operations that are very useful; these includes bit selection and concatenation.

1. Bit selection: The bits in a bit-vector can be selected by a bit selection expression, with the syntax:

bit-vector-name [ integer ] , for selecting a single bit and

bit-vector-name [ integer1, integer2 ] for selecting a range of bits.

For example, if BV is a bit-vector(7,0) of value "00011101", then BV[0] selects the least significant bit, which is '1'; BV[7,4] selects the most significant four bits, which are "0001".

2. Concatenation: Two bit-vectors can be concatenated into a new bit-vector by operator "@". The new bit-vector's width is the sum of the two primitive bit-vectors; it is labeled as bit-vector(width-1,0) regardless of how the two primitive bit-vectors are labeled. For example, if b1(3,0) is "0111" and b2(3,0) is "1010", then b1 @ b2 is "01111010" and is labeled as (7,0). If b1 and b2 are labeled differently but keep the same values, b1 @ b2 is unchanged.

Bit-vector concatenation can not only be used in expressions, such as in b3: = b1 @ b2, but can also be used for pattern matching in the left-hard side of signal assignments. The example in Figure 2.4 uses bit-vector concatenation and describes an adder with carry output. Inputs a and b are bit-vectors of the same width (assume the width is w1). sum is the sum result of width w1 and carry is the 1-bit carry output.

```

width ...

hw adder (a, b, sum, carry:bit) =

carry @ sum := a + b

```

Figure 2.4: HML description of an adder with carry output using bit-vector concatenation

Concatenation is not supported by the HML system yet.

#### 2.3.3.3 Behavioral Operators

There are a couple of operators that operate on behavior type. Behavior operator "||" is used to compose several submodules into one hardware module – in structural descriptions, the submodules are instance of hardware functions and have type of behavior; in behavioral descriptions, the submodules are concurrently running behaviors. The submodules (in either structural format or behavioral format) communicate via signals. Structural and behavioral descriptions can be mixed by "||".

Operator ";" is used inside a behavioral description to compose multiple behavioral expressions into a behavior. ";" is also used in software functions, as the sequential expressions composer; in this case, ";" operates on any type except behavior. The use of ";" in software functions will be discussed in Section 2.3.3.4.

Behavioral operators "||" and ";" have the same hardware meanings. For example,

```

hw ... = s:=1; t:=2 and

hw .. = s:=1 || t:=2

```

are equivalent. The difference is syntax: "||" is only allowed in the top-level of a hardware function to compose either behaviors or structural modules; the HML parser treats behaviors composed with "||" as independent processes. ";" is usually used inside a behavior at a lower level when the behavior has multiple expressions

in it. For example,

```

hw ...= if condition then (s:=1; t:=2) else ...

```

is valid in HML; the ";" used here is not replaceable by "||" because it appears inside an *if-then-else* expression but not at the top-level. Users can make use of the syntax difference to organize their programs: use "||" to partition the whole circuit into several sub-modules; use ";" while describing each sub-module.

While using "||" and ";" to compose behavior expressions, the order is not important because all the behavior expressions execute concurrently.

#### 2.3.3.4 Expressions

In addition to the operators described above, HML has following constructs for expressions. Key words are **bold-faced**.

- If-then-else expression: if exp1 then exp2 [else exp3].

The else part is optional.

- Let-in-end expression: let decls in exp end.

decls is multiple declarations.

- Case expression:

```

case exp of rule\ list, rule: pat => exp.

```

If multiple expressions are use in any place where one *exp* appears, they must be enclosed by " ( " and " ) ", and they are separated by ";". In software functions, these expressions can have different types and they are evaluated in order; the result for the whole expression is that of the last expression in the sequence. In hardware functions, these expressions must have the type of *behavior*.

Signal assignments are expressions which are of behavior type. This has been discussed in Section 2.3.2.

Functions in HML are abstract values; They need not have a name. HML allows anonymous functions with fn notation as shorthand for function declarations. fn is an expression which has function type, it defines an anonymous software function. The syntax is:

Fn expression: fn  $rule\ list$ . The definition of  $rule\ list$  is the same as defined in Case expression.

For example, fn = n \* 2 is a function of type  $int \to int$  that doubles an integer. It is an anonymous form for function defined by:

fun double(n) = n \* 2.

Fn expressions can be applied to an argument; (fn n=> n \* 2)(9) applies the function defined by (fn n=> n\*2 to an integer argument 9. Anonymous functions can be given a name by a val declaration. val double = fn n=> n \* 2 is equivalent to fun double(n) = n \* 2.

Note that fn notation only defines software functions.

#### 2.3.4 Function and Hardware Function Declarations

There are two kinds of functions in HML, the software functions and hardware functions, as discussed in Section 2.2.2. The types of them have been addressed in Section 2.2.2. Here we look at their syntax and difference.

The syntax for function and hardware function declarations are very similar except the two have different keywords **fun** and **hw**. The syntax is:

$fun\_hw\_dec: \mathbf{fun/hw} \ clauses$

clauses : clause

clause clauses

clause : id pats  $[: result\_type] = exp.$

Note that in software or hardware function declarations, the types of arguments and results do not need to be declared. The user can choose to declare all of them or some of them; this is useful particularly when some types can not be resolved by the type checker. For example,

fun sum

$$(a, b) = a+b$$

defines a polymorphic adder that can operates on *integer* or *bit-vector* types. A user who wants an integer adder can write:

fun sum

$$(a:int, b) = a+b$$

which declares input a to have integer type, or

fun sum

$$(a, b)$$

: int = a+b

which declares the return value to have integer type.

Semantically, the major difference between the two kind of declarations is that hardware functions represent hardware modules, while software functions are for software use. They can be called in hardware functions, and are used only as an aid to hardware functions. Another difference is that a software function returns values of a specific type other than behavior type, and a hardware function must return behavior type (which means the expression in the hardware function declaration must be composed by signal assignments or other hardware modules). Hardware function declarations are the major parts of an HML program; how to declare hardware functions will be covered in greater detail in Section 2.4.

# 2.4 Describing Hardware in HML

HML is a declarative language. Figure 2.5 shows that the top level of HML programs are a series of declarations, including value declarations, type declarations, function declarations and hardware declarations. Hardware declarations introduce a special kind of function which represents hardware modules; they are the main part of HML descriptions.

HML hardware functions can be used to declared structures or behaviors or the mixture of both structures and behaviors.

Figure 2.5: HML programming constructs and program organization – a simplified HML abstract syntax tree

# 2.4.1 Describing Structure in HML

HML structures are built from modules and signals. Modules may either be primitive modules or compound modules built using the module composition operator "||". Primitive modules are predefined hardware functions described with structural or behavioral HML. HML provides a small predefined library of basic gates that can be used to build other structures. Signals with the same name are connected. Signals internal to a module are declared using the intern keyword and scoped by let...in...end. The arguments of the modules are signals.

In Section 2.1.3, we have seen a 1-bit full adder described in structural HML: given the two-input gates AND, OR and XOR have been defined, a one bit full adder is defined as an interconnection of these primitives. This kind of structural description is straightforward. It is like a language version of the schematic: list all the submodules and draw the connections. Other languages that support structural level descriptions such as VHDL also use similar formats, although the actual

syntax may vary. However, since a hardware module can be an argument of another hardware function, HML structural descriptions can be more complicated and more flexible than a simple netlist.

Using the structural format, functions for regular structure generators can be written in HML by exploiting polymorphism and high order functions. These can then be applied to different types of cells. We have written generators for different kinds of arrays and trees. In VHDL and other HDLs that do not support polymorphism and high order functions, the user has to write the same generators several times if the type of the cell structures or the number of the cells is different.

Example. The array generator is independent of the actual types of its cells. A hardware function array instantiates n copies of cell connected to buses inp and outp. See Figure 2.6. This array generator is polymorphic: cell can be of any module with an input and an output port that can be of any width; inp and outp are bit-vectors of any width.

```

hw array 1 cell inp outp =

cell (inp[0], outp[0])

| array n cell inp outp =

cell (inp[n-1], outp[n-1])

| array (n-1) cell (inp, outp))

```

Figure 2.6: Example: A polymorphic array generator

**Example.** Based on the 1-bit full adder described in Section 2.1.3, we can write an n-bit full adder generator (see Figure 2.7). If the 1-bit full adder is generalized to other cells with the same interface, then the following description becomes a generator of a ripple array with outputs.

Note that for high-order and recursive functions, we only implement type checking but not the translation to VHDL. This will be discussed in detail in Section 4.3.

```

hw adder-array(1, fullAdder, a, b, cin, sum, cout) =

fullAdder (a[0], b[0], cin, sum[0], cout)

| adder-array(n, fullAdder, a, b, cin, sum, cout) =

let

intern carry

in

fullAdder (a[n-1], b[n-1], carry, sum[n-1], cout)

|| adder-array(n-1, fullAdder, a, b, cin, sum, carry)

end

```

Figure 2.7: An n-bit full adder generator based on a 1-bit full adder

## 2.4.2 Describing Behavior in HML

A behavior is a group of hardware description expressions based on signal assignments. Inside a behavior, the hardware description expressions are evaluated sequentially in zero time in each evaluation cycle. HML has a behavior composer "||" that combines several concurrently executing behaviors into a hardware function of a behavior type.

**Example.** The simple adder shown in Figure 2.8 can operate on various types (integer, bit or bit-vector). The assignment s1 := a + b specifies a combinational adder and s2 <- s1 specifies that the output s1 will be latched in a register.

```

hw sum (a, b, s1, s2) = s1 := a + b | s2 <- s1

```

Figure 2.8: Example: A polymorphic adder with latched output

The program doesn't specify a clock, but the "<-" signifies a register assignment which implies that a clock signal is needed in the hardware. Also no variable or signal declarations are needed and the arguments of the top level function represent the interface (inputs and outputs) to the hardware described.

## 2.4.3 Putting Behaviors and Structures Together

In the previous sections we have discusses how to describe behaviors and structures in HML. Sometimes it is convenient to mix behavioral descriptions and structural descriptions. Mixing behavioral and structural descriptions is particularly useful when users try to build new programs based on some predefined hardware functions (modules) – the predefined hardware functions can be used directly in a structural format while new descriptions are added in either structural or behavioral format.

Assuming we have predefined an add hardware function,

```

hw add (x, y, z) = z := x + y,

```

the polymorphic adder with latched output in Figure 2.8 can be rewritten by mixing structural and behavioral descriptions, as shown in Figure 2.9.

Figure 2.9: Rewrite the polymorphic adder with latched output by mixing structural and behavioral descriptions

Figure 2.5 summarizes the basic programming facilities and program organization of HML. It is a simplified HML abstract syntax tree. For greater detail on the syntax of HML, refer to Appendix A.

# 2.4.4 Restrictions of Describing Hardware in HML

There are some restrictions that users should follow in order to write correct HML hardware descriptions.

No combinational loops are allowed: combinational loops do not have specific hardware meanings. For example, if there exist two combinational signal assignments s:=t and t:=s, the type checker will detect this as an error. However, s:=t and  $t\leftarrow s$  can appear in the same program because the register assignment  $t\leftarrow s$

introduces a delay (a clock cycle). In real programs, combinational loops may have more complicated formats; the detection of such loops is done by detecting whether there is any cycle in the signal dependency graph for combinational signal assignments only.

Multiple assignments to the same signal are illegal in HML. Since all the signal assignments run concurrently, multiple assignments to the same signal can not be resolved and therefore are not allowed. The idea for implementing this restriction is simple – to detect whether the left-hand side signal in a signal assignment appears in the left-hand side of other signal assignments. In the case of mixing structural and behavioral descriptions, it is a little more complicated. Consider the example in Figure 2.10; s1 appears to be assigned only once, but it is also the output of AND(a, b, s1). In this case s1 actually gets assigned twice. Therefore the strategy to detect multiple assignments is generalized to detect not only whether a signal appears at the left-hand side of an assignment but also whether it is an output of a structural expression.

```

hw example (a, b, c, s1, s2) =

AND (a, b, s1)

|| s1 := a + b

|| s2 := a OR c

```

Figure 2.10: Example of multiple assignments to one signal

### 2.5 Discrepancies Between HML and SML

As discussed in previous sections of this Chapter, HML inherited a big part of its syntax from SML. However, HML differs somewhat from the syntax inherited from SML. Users who have used SML before can avoid confusion by following these guidelines. Users who do not have SML experience can ignore this section.

• Functions: SML allows two formats for defining functions of multiple arguments. For example, for an Add1 function that adds two values, both

fun Add2 x y = x + yand fun Add (x, y) = x + y

are acceptable. The two Add functions defined have different types: the former format has type  $\alpha \to (\alpha \to \alpha)$ ; the latter has type  $\alpha * \alpha \to \alpha$ . The former format defines a curried function [Pau91] and permits partial application. In our example, if Add1 is applied to its first argument (of type  $\alpha$ ) its result is a function of type  $\alpha \to \alpha$ . As in SML, HML also allows these two formats of defining functions of multiple arguments. HML however does not support the feature of curried functions and the two formats define functions of the same type:  $\alpha * \alpha \to \alpha$ . Partial application is not supported in HML.

- **Keyword AND:** In HML the declaration construct val... and val ... is not permitted and keyword and is reserved as a logical operator.

- Let-in-end: In the let-decl-in-exps-end construct, the multiple expressions exps doesn't need to be put in parentheses; but in HML, they have to be put in parentheses. For example, let .. in exp1; exp2; exp2 end is valid in SML, but in HML, only let .. in (exp1; exp2; exp2) end is permitted.

## Chapter 3

# HML Type Checking and

## Inference

This chapter examines type checking and type inference in HML. The type checking rules and the algorithm are discussed.

### 3.1 Introduction

Since HML is a polymorphic, high-order programming language, type checking and type inference are more important and complicated than for a language with a monomorphic type system and no high-order functions.

The task of the type checker is to check that an expression has a particular type or to infer a most general type for it if its type can not be decided. A type inference algorithm can be constructed for deducing the types of expressions from the types of primitive operations [Rea89].

One of the principal goals of HML is to catch errors as early in the design process as possible. This is done by performing some design rule checking as part of type checking. The design rule checking done by the HML type checker is mostly interface checking: if a signal or a bus connected to a hardware module does not match its port type, then an error occurs.

The type inference information is very crucial for HML to connect to any back end. In the HML-to-VHDL translator that will be described in the next chapter, type information is added to all VHDL declarations.

## 3.2 Type Checking and Type Inference Rules

### 3.2.1 Definition of Types Used in the Type Checker

The definition of types (see Figure 3.1) in the type checker not only includes the general meaning of types, which is called *pure types* here, but also includes *modes* in types, so that we can tell whether an expression has a **constant** mode or a **variable** mode. The difference is that an expression of *constant* mode can not be assigned to. The following classes of type metavariables are needed to show the type checking and type inference rules of HML:

- 1. Modes  $\mu$ : Ranges over modes; either constant or variable.

- 2. Pure types  $\pi$ : Ranges over types without modes attached, for example, int or bool.

- 3. Types  $\tau$ : A type is a mode plus a pure type; that is, every  $\tau$  can be expressed in the form  $\mu\pi$ , such as constant int.

- 4. In/Out  $\iota$ : This is used in *hardware* types only, to indicate whether a port of the hardware is input, output, or a bidirectional port.

Because of the polymorphism of the type system, the possible forms of type are extended to include type variables  $\alpha$ ,  $\beta$ ,  $\gamma$ , ...

```

\begin{array}{lll} \mu & := & \operatorname{constant} \mid \operatorname{variable} \\ \pi & := & \operatorname{unit} \mid \operatorname{bool} \mid \operatorname{int} \mid \operatorname{bit} \mid \operatorname{behavior} \\ \mid & \operatorname{bit\_vector} \left( i : \operatorname{int}, j : \operatorname{int} \right) \\ \mid & \operatorname{function} \left( \pi_1, \, ..., \, \pi_n \right) \to \pi \quad \text{where n} \geq 0 \\ \mid & \operatorname{hardware} \left( \, \iota_1 \pi_1, \, ..., \, \iota_n \pi_n \right) \to \operatorname{behavior} \quad \text{where n} > 0 \\ \iota & := & \operatorname{input} \mid \operatorname{output} \mid \operatorname{inout} \mid \operatorname{not\_applied} \\ \tau & := & \mu \pi \end{array}

```

Figure 3.1: Definition of types: modes and pure types

### 3.2.2 Environments

We need to keep track of the types of all the objects; they are included in type environments, which are simply partial functions from objects to types. While describing type checking rules, **A** is used to represent environments.

### 3.2.3 Type Inference Rules

The rules for the polymorphic type inference system are summarized in Figure 3.2 [Rea89]. This section explains all the type inference rules individually.

Before explaining the inference rules in Figure 3.2, we look at the notation used to describe the rules. In expression "A  $\vdash E : \mu \pi$ ", "A" is the environment discussed in Section 3.2.2, E is an expression, and  $\mu \pi$  is the mode and pure type. "A  $\vdash E : \mu \pi$ " means that in environment A, expression E has mode  $\mu$  and type  $\pi$ .

**1.Signal**

$$A \vdash V : S$$

when  $A(V) = S$

**2.Constant**  $A \vdash C : S$  when  $A(C) = S$

Rule 1 and 2 indicate that to check what type an identifier has, look it up in the environment. In HML, an identifier can be either a signal or a constant.

3. Arithmetic, logical

$$A \vdash E_1 : \mu_1 \pi$$

$A \vdash E_2 : \mu_2 \pi$  & boolean exps  $A \vdash E_1 \star E_2 : \text{constant } \pi$

0. Notation

$$A \vdash E : \mu\pi$$

1. Signal

$$A \vdash V : S \quad \text{when } A(V) = S$$

2. Constant

$$A \vdash C : S \quad \text{when } A(C) = S$$

3. Arithmetic, logical &

$$A \vdash E_1 : \mu_1\pi \quad A \vdash E_2 : \mu_2\pi$$

& boolean exps

$$A \vdash E_1 : \mu_1\pi \quad A \vdash E_2 : \mu_2\pi$$

$$A \vdash E_1 : \mu_1\pi \quad A \vdash E_2 : \mu_2\pi$$

$$A \vdash E_1 : \mu_1\pi \quad A \vdash E_2 : \mu_2\pi$$

$$A \vdash E_1 : \mu_1\pi \quad A \vdash E_2 : \mu_2\pi$$

$$A \vdash E_1 : \mu_1\pi \quad A \vdash E_2 : \mu_2\pi$$

$$A \vdash E_1 : \mu_1\pi \quad A \vdash E_2 : \mu_2\pi$$

$$A \vdash E_1 : \mu_1 \Rightarrow A \vdash E_2 : \mu_2\pi$$

$$A \vdash E_1 : \mu_1 \Rightarrow A \vdash E_2 : \mu_2\pi \quad A \vdash E_3 : \mu_3\pi$$

$$A \vdash \text{if } E_1 \text{ then } E_2 \text{ else } E_3 : \text{constant } \pi$$

6. If-then-else

$$A \vdash E_1 : \mu_1 \Rightarrow A \vdash E_2 : \mu_2\pi \quad A \vdash E_3 : \mu_3\pi$$

$$A \vdash \text{if } E_1 \text{ then } E_2 \text{ else } E_3 : \text{constant } \pi$$

7. Case

$$\text{expression} \quad A \vdash E' : \mu_1\pi \quad A \vdash E' : \mu_2\pi \quad A \vdash E' : \mu_2\pi$$

Figure 3.2: HML type checking and type inference rules

The types of composite expressions are built from the types of their subterms. Rule 3 explains the type inference for arithmetic, logical and boolean expressions. Let  $\star$  be any operator of the above classes. The rule says that the two sub-expressions can have any mode  $\mu 1$  and  $\mu 2$ , but they must have the same type  $\pi$ ; the result expression has **constant** mode (for example,  $\mathbf{x}+\mathbf{y}$  has constant mode –  $\mathbf{x}+\mathbf{y}:=1$  is not a valid expression), and type  $\pi$  - the type of the two sub-expressions.

4.Relational

$$A \vdash E_1 : \mu_1 \pi$$

$A \vdash E_2 : \mu_2 \pi$  expressions  $A \vdash E_1 \star E_2 : \text{constant bool}$

Type inference rule for relational expressions (**rule 4**) is similar to rule 3 – it requires that the two sub-expressions to have the same type but not necessarily the same mode. The result expression has constant mode and *boolean* type.

5.Signal

$$A \vdash E_1 : \text{variable } \pi$$

$A \vdash E_2 : \mu \pi$  assignments  $A \vdash E_1 := / \leftarrow E_2 : \text{constant behavior}$

For signal assignments (either combinational or sequential), as in **rule 5**, the left-hand side and right-hand side sub-expressions should have matching types; the mode of the left-hand side expression must be **constant** mode. The result expression is of *behavior* type, as discussed in Section 2.3.2.

6.If-then-else

$$A \vdash E_1 : \mu_1 \text{ bool } A \vdash E_2 : \mu_2 \pi \ A \vdash E_3 : \mu_3 \pi$$

$A \vdash \text{if } E_1 \text{ then } E_2 \text{ else } E_3 : \text{ constant } \pi$

If-then-else expressions also require matching types; the type of the condition must be boolean (rule 6).

7.Case

$$\begin{array}{c} A \vdash E^{'} : \mu^{'}\pi^{'} \ A + [\ V : \mathbf{constant}\ \pi^{'}\ ] \vdash E : \mu\pi \\ \\ \mathbf{expression} \end{array}$$

$$A \vdash \mathbf{case}\ E^{'}\ \text{of}\ \mathbf{V} \Rightarrow E : \mathbf{constant}\ \pi$$

In a case expression (rule 7) case E' of  $V \Rightarrow E$ , expression E' and its case V should have the same type; the result expression type is the type of case body expression E. The real case expression usually has multiple clauses; cases and body expressions in different clauses should be compared to each other to guarantee matching types. Type information of one clause can also be used to infer types of another clause.

8.Function

$$A \vdash E : \mu_1 \quad \pi' \to \pi \quad A \vdash E' : \mu_2 \pi'$$

application  $A \vdash EE' : \mathbf{constant} \quad \pi$

A function expression has type  $\pi' \to \pi$  where  $\pi'$  is a list of the types of the arguments and  $\pi$  is the return type. In a function application (**rule 8**), assuming the type of the function is  $\pi' \to \pi$ , the arguments are checked to have type  $\pi'$ ; the result expression has type  $\pi$  and constant mode.

9.Let-in-end

$$A \vdash E' : S$$

$A + [V : S] \vdash E : \mu \pi$

$A \vdash \text{let val } V = E' \text{ in } E \text{ end } : \text{constant } \pi$

The type inference rule for let-in-end expressions (rule 9) is more complicated because the declarations in a let-decls-in-exp-end expression introduce new bindings and therefore the body expression exp should be evaluated in a new environment. The result expression type is the type of the body expression.

10.Function

$$A + [V : \mathbf{constant} \ \pi'] \vdash E : \mu\pi$$

abstraction  $A \vdash \text{fn } V \Rightarrow E : \mathbf{constant} \ \pi' \to \pi$

Function abstraction (fn-expression) is similar to the let-in-end expression because it also involves new bindings. In expression fn  $V \Rightarrow E$ , function argument V should be added into the old environment A while evaluating body expression E. If the type of V is inferred as  $\pi'$  and the type of E is  $\pi$ , the result expression has

function type  $\pi' \to \pi$ . Like case expressions, function abstractions may have multiple clauses; these clauses should be compared each other to guarantee matching types.

## 3.3 Type Checking and Inference Algorithm

The basic approach of the type checking and inference algorithm involves two processes: **bottom-up** and **top-down**.

The type checking and inference starts from the leaves of the abstract syntax tree, applies the type rules in Figure 3.2 to check whether the types of the primitives fit the requirement of the rules and to infer unknown types – including types of the parent and the siblings in the abstract syntax tree. For example, in expression e1+e2, if subexpression e1 is checked to have type *integer*, then we can infer that e2 (sibling) as well the composite expression e1+e2 (parent) have the same type *integer*.

If a type can not be decided in the bottom-up process, it will be assigned a type variable as its type. If the type of an element in the abstract syntax tree is inferred by checking a type rule, the top-down process is applied to recheck the types of elements that are under the current element in the abstract syntax tree as well as its siblings. Associated with each element is a boolean attribute called decided which indicates whether the types of the elements under this elements have been decided. If decided is true, there is no need to initiate the top-down process. Top-down processes use the same rules as bottom-up processes, except conditions and results of the rules are reversed.

The processes can be illustrated with the following example.

```

fun type_example (a,b,c,d) = (a+b) + (c+d) + 1

```

The abstract syntax tree segment for expression (a+b) + (c+d) + 1 is shown

in Figure 3.3.

Figure 3.3: Abstract syntax tree segment for expression (a+b)+(c+d)+1

The type checker has to infer the types of arguments a, b, c and d as well as the type of function type\_example. When names a, b, c and d are first introduced as the arguments of function type\_example, their types are unknown and they are given type variables  $\alpha 1$ ,  $\alpha 2$ ,  $\alpha 3$  and  $\alpha 4$  as their type expressions. The integer 1 has type int. The type inference starts from the bottom-up process. Node n1:a+b is checked first according to type inference rule 3 in Figure 3.2. Since a and b should have same type, the type expression of b  $(\alpha 2)$  is replaced by that of a  $(\alpha 1)$  and the type of node n1 is  $\alpha 1$ . Similarly node n2:c+d is checked and c and d as well as node n2 have type  $\alpha 3$ . Going up from node n1 and n2, node n3:n1+n2 can be type-checked. Since n1:(a+b) and n2:(c+d) should the same type, the type of n2:(c+d)  $\alpha$ 3 is therefore replaced by the type of n1:(a+b)  $\alpha$ 1. This initiates a top-down process to update the types of c and d according to the updated type of n2:c+d. In the top-down process, c and d are updated to have type expression  $\alpha 1$ . Node n3 has type  $\alpha 1$ . Then the bottom-up process restarts to check node n4:n3+1. The integer 1 force node n4 as well as node n3 to have integer type. The updating of n3 initiates another top-down process to update the types of nodes under n3; a, b, c and d are updated to have integer type. The above type inference procedures are summarized with the following steps:

#### Bottom-up Steps

- **0.** Leaves a: $\alpha$ 1, b: $\alpha$ 2, c: $\alpha$ 3, d: $\alpha$ 4, 1:int

- 1. n1 a+b: $\alpha$ 1, update b: $\alpha$ 1

- 2. n2 c+d: $\alpha$ 3, update d: $\alpha$ 3